Kaikkein edistyksellisimmät puolijohdepiirit valmistetaan tällä hetkellä 14 nanometrin viivanleveydellä. Arvioiden mukaan suurimmat puolijohdevalmistajat siirtyisivät 10 nanometrin tuotantotekniikkaan ensi vuoden loppupuoliskolla ja seitsemään nanometriin ehkä jo vuonna 2017.

TSMC on kertonut suunnitelmistaan tuottaa piirejä seitsemän nanometrin tekniikalla vuonna 2017, mutta se ei ole ainakaan julkisesti vielä esitellyt sillä tuotettuja toimivia piirejä. Intel on myös puhunut siirtyvänsä transistoreissa pois piistä ja käyttävänsä uusia materiaaleja 7 nm:n tekniikalla tuotetuissa transistoreissa.

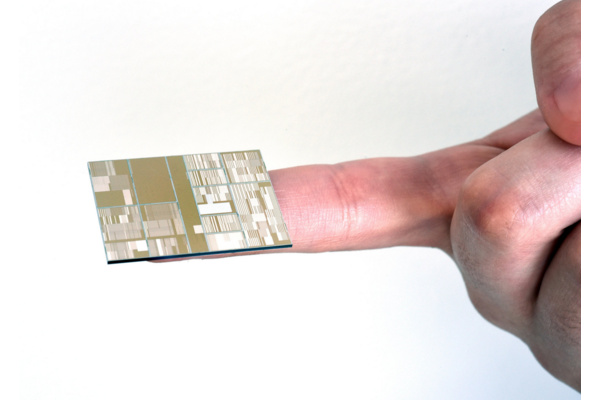

IBM:n yhteistyökumppaneita tuotantotekniikan kehityksessä olivat GlobalFoundries, Samsung ja SUNY Polytechnic Instituten Colleges of Nanoscale Science and Engineering. IBM ei lähtenyt vielä arvioimaan koska tekniikka olisi valmis kaupallistettavaksi.

Kirjoittaja: Manu Pitkänen @ 9. heinäkuuta, 2015 12:12